# Lecture Notes in Computer Science 1656 Edited by G. Goos, J. Hartmanis and J. van Leeuwen

# Springer Berlin

Berlin

Heidelberg

New York

Barcelona

Hong Kong

London

Milan

Paris

Singapore

Tokyo

Siddhartha Chatterjee Jan F. Prins Larry Carter Jeanne Ferrante Zhiyuan Li David Sehr Pen-Chung Yew (Eds.)

# Languages and Compilers for Parallel Computing

11th International Workshop, LCPC'98 Chapel Hill, NC, USA, August 7-9, 1998 Proceedings

#### Volume Editors

Siddhartha Chatterjee, Jan F. Prins

Department of Computer Science, The University of North Carolina

Chapel Hill, NC 27599-3175, USA

E-mail: {sc/prins}@cs.unc.edu

Larry Carter, Jeanne Ferrante

Department of Computer Science and Engineering

University of California at San Diego

9500 Gilman Drive, La Jolla, CA 92093-0114, USA

E-mail: {carter/ferrante}@cs.ucsd.edu

Zhiyuan Li

Department of Computer Science, Purdue University

1398 Computer Science Building, West Lafayette, IN 47907, USA

E-mail: li@cs.purdue.edu

David Sehr

**Intel Corporation**

2200 Mission College Boulevard, RN6-18, Santa Clara, CA 95052, USA

E-mail: dsehr@gomez.sc.intel.com

Pen-Chung Yew

Department of Computer Science and Engineering, University of Minnesota

Minneapolis, MN 55455, USA

E-mail: yew@cs.umn.edu

Cataloging-in-Publication data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

#### Languages and compilers for parallel computing: 11th

international workshop; proceedings / LCPC '98, Chapel Hill, NC, USA, August 7 - 9, 1998. S. Chatterjee ... (ed.). - Berlin; Heidelberg

; New York; Barcelona; Hong Kong; London; Milan; Paris;

Singapore; Tokyo: Springer, 1999

(Lecture notes in computer science; Vol. 1656)

ISBN 3-540-66426-2

CR Subject Classification (1998): D.1.3, D.3.4, F.1.2, B.2.1, C.2

ISSN 0302-9743

ISBN 3-540-66426-2 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

© Springer-Verlag Berlin Heidelberg 1999 Printed in Germany

Typesetting: Camera-ready by author

SPIN: 10704088 06/3142 – 5 4 3 2 1 0 Printed on acid-free paper

### Steering Committee

Utpal Banerjee Intel Corporation

David Gelernter Yale University

Alex Nicolau University of California at Irvine

David Padua University of Ilinois at Urbana-Champaign

#### **Program Committee**

Larry Carter University of California at San Diego

Siddhartha Chatterjee University of North Carolina at Chapel Hill

Jeanne Ferrante University of California at San Diego

Zhiyuan Li Purdue University

Jan Prins University of North Carolina at Chapel Hill

David Sehr Intel Corporation

Pen-Chung Yew University of Minnesota

## Organizing Committee

Linda Houseman University of North Carolina at Chapel Hill

#### External Reviewers

George Almasi Asheesh Khare

Ana Azevedo Jaejin Lee

Brian Blount Yuan Lin

Calin Cascaval Yunheung Paek

Walfredo Cirne Nick Savoiu

Paolo D'Alberto Martin Simons

Vijay Ganesh Weiyu Tang

Xiaomei Ji

#### VI Preface

LCPC'98 Steering and Program Committee for their time and energy in reviewing the submitted papers. Finally, and most importantly, we thank all the authors and participants of the workshop. It is their significant research work and their enthusiastic discussions throughout the workshop that made LCPC'98 a success.

May 1999

Siddhartha Chatterjee Program Chair

#### **Preface**

The year 1998 marked the eleventh anniversary of the annual Workshop on Languages and Compilers for Parallel Computing (LCPC), an international forum for leading research groups to present their current research activities and latest results. The LCPC community is interested in a broad range of technologies, with a common goal of developing software systems that enable real applications. Among the topics of interest to the workshop are language features, communication code generation and optimization, communication libraries, distributed shared memory libraries, distributed object systems, resource management systems, integration of compiler and runtime systems, irregular and dynamic applications, performance evaluation, and debuggers. LCPC'98 was hosted by the University of North Carolina at Chapel Hill (UNC-CH) on 7 - 9 August 1998, at the William and Ida Friday Center on the UNC-CH campus. Fifty people from the United States, Europe, and Asia attended the workshop.

The program committee of LCPC'98, with the help of external reviewers, evaluated the submitted papers. Twenty-four papers were selected for formal presentation at the workshop. Each session was followed by an open panel discussion centered on the main topic of the particular session. Many attendees have come to regard the open panels as a very effective format for exchanging views and clarifying research issues. Using feedback provided both during and after the presentations, all of the authors were given an opportunity to improve their papers before submitting the final manuscript contained in this volume. This collection documents important research activities from the past year in the design and implementation of programming languages and environments for parallel computing.

The major themes of the workshop included both classical issues (Fortran, instruction scheduling, dependence analysis) as well as emerging areas (Java, memory hierarchy issues, network computing, irregular applications). These themes reflect several recent trends in computer architecture: aggressive hardware speculation, deeper memory hierarchies, multilevel parallelism, and "the network is the computer." In this final editing of the workshop papers, we have grouped the papers into these categories.

In addition to the regular paper sessions, LCPC'98 featured an invited talk by Charles Leiserson, Professor of Computer Science at the MIT Laboratory for Computer Science, entitled "Algorithmic Multithreaded Programming in Cilk". This talk was the first exposure to the Cilk system for many of the participants and resulted in many interesting discussions. We thank Prof. Leiserson for his special contribution to LCPC'98.

We are grateful to the Department of Computer Science at UNC-CH for its generous support of this workshop. We benefited especially from the efforts of Linda Houseman, who ably coordinated the logistical matters before, during, and after the workshop. Thanks also go out to our local team of volunteers: Brian Blount, Vibhor Jain, and Martin Simons. Special thanks are due to the

# **Table of Contents**

| Java                                                                                                 |

|------------------------------------------------------------------------------------------------------|

| From Flop to MegaFlops: Java for Technical Computing                                                 |

| Considerations in HPJava Language Design and Implementation                                          |

| Locality                                                                                             |

| A Loop Transformation Algorithm Based on Explicit Data Layout Representation for Optimizing Locality |

| An Integrated Framework for Compiler-Directed Cache Coherence and Data Prefetching                   |

| I/O Granularity Transformations                                                                      |

| Network Computing                                                                                    |

| Stampede: A Programming System for Emerging Scalable Interactive Multimedia Applications             |

| Network-Aware Parallel Computing with Remos                                                          |

| Object-Oriented Implementation of Data-Parallelism on<br>Global Networks                             |

| Fortran                                                                                              |

| Optimized Execution of Fortran 90 Array Language on<br>Symmetric Shared-Memory Multiprocessors       |

## X Table of Contents

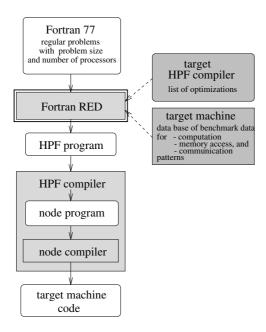

| Fortran RED — A Retargetable Environment for<br>Automatic Data Layout                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Automatic Parallelization of C by Means of Language Transcription 166 Richard L. Kennell and Rudolf Eigenmann (Purdue University)                                                                 |

| Irregular Applications                                                                                                                                                                            |

| Improving Compiler and Run-Time Support for Irregular Reductions Using Local Writes                                                                                                               |

| Beyond Arrays — A Container-Centric Approach for<br>Parallelization of Real-World Symbolic Applications                                                                                           |

| SIPR: A New Framework for Generating Efficient Code for<br>Sparse Matrix Computations                                                                                                             |

| HPF-2 Support for Dynamic Sparse Computations                                                                                                                                                     |

| Instruction Scheduling                                                                                                                                                                            |

| Integrated Instruction Scheduling and Register Allocation Techniques247 David A. Berson (Intel Corporation), Rajiv Gupta (University of Pittsburgh) and Mary Lou Soffa (University of Pittsburgh) |

| A Spill Code Placement Framework for Code Scheduling                                                                                                                                              |

| Copy Elimination for Parallelizing Compilers                                                                                                                                                      |

| Potpourri                                                                                                                                                                                         |

| Compiling for SIMD Within a Register                                                                                                                                                              |

| Automatic Analysis of Loops to Exploit Operator Parallelism on<br>Reconfigurable Systems                                                                                                          |

| Principles of Speculative Run–Time Parallelization                                                                                                                                                |

| Dependence Analysis                                                         |

|-----------------------------------------------------------------------------|

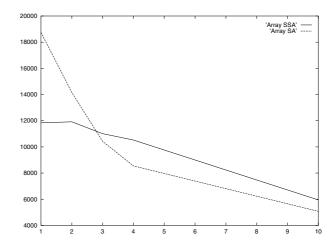

| The Advantages of Instance-Wise Reaching Definition Analyses in Array (S)SA |

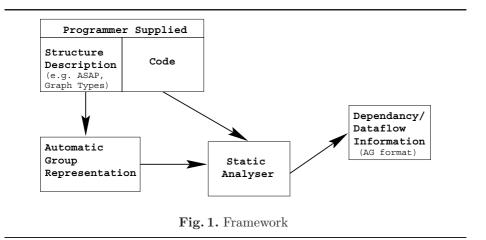

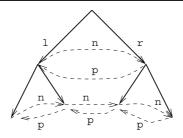

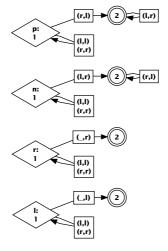

| Dependency Analysis of Recursive Data Structures Using Automatic Groups     |

| The I+ Test                                                                 |

| Author Index                                                                |

# From Flop to MegaFlops: Java for Technical Computing

J. E. Moreira, S. P. Midkiff, and M. Gupta

IBM T.J. Watson Research Center

P.O. Box 218, Yorktown Heights, New York 10598, USA

{jmoreira,smidkiff,mgupta}@us.ibm.com

Abstract. Although there has been some experimentation with Java as a language for numerically intensive computing, there is a perception by many that the language is not suited for such work. In this paper we show how optimizing array bounds checks and **null** pointer checks creates loop nests on which aggressive optimizations can be used. Applying these optimizations by hand to a simple matrix-multiply test case leads to Java compliant programs whose performance is in excess of 500 Mflops on an RS/6000 SP 332MHz SMP node. We also report in this paper the effect that each optimization has on performance. Since all of these optimizations can be automated, we conclude that Java will soon be a serious contender for numerically intensive computing.

#### 1 Introduction

The scientific programming community has recently demonstrated a great deal of interest in the use of Java for technical computing. There are many compelling reasons for such use of Java: a large supply of programmers, it is object-oriented without excessive complications (in contrast to C++), and it has support for networking and graphics. Technical computing is moving more and more towards a network-centric model of computation. In this context, it can be expected that Java will first be used where it is most natural: for visualization and networking components. Eventually, Java will spread into the core computational components of technical applications.

Nevertheless, a major obstacle remains to the pervasive use of Java in technical computing: performance. Let us start by looking into the performance of a simple matrix-multiply routine in Java, as shown in Fig. 1. This routine computes  $C = C + A \times B$ , where C is an  $m \times p$  matrix, A is an  $m \times n$  matrix, and B is an  $n \times p$  matrix. We use that routine to multiply two  $500 \times 500$  matrices (m = n = p = 500) on an RS/6000 SP 332MHz SMP node. This machine contains  $4 \times 332$  MHz PowerPC 604e processors, each with a peak performance of 664 Mflops. We refer to this simple benchmark as MATMUL.

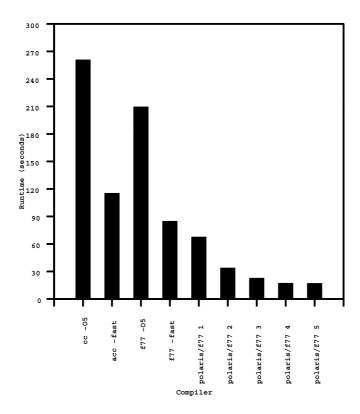

The Java code is compiled into a native executable by the IBM High Performance Compiler for Java (HPCJ) [10], and achieves a performance of 5 Mflops on a 332 MHz PowerPC 604e processor. The equivalent Fortran code, compiled by the IBM XLF compiler, achieves 265 Mflops! A 50-fold performance

Fig. 1. Simple matrix-multiply code in Java.

degradation makes it hard to justify using Java for a technical application. The single-threaded version of ESSL (Engineering and Scientific Subroutine Library [22]), carefully hand-tuned to achieve optimum performance, executes the matrix multiplication at 289 Mflops. The multi-threaded version of ESSL achieves 1183 Mflops!

Why is the performance of Java so bad, relative to Fortran? In the case of matrix-multiply, the IBM XLF Fortran compiler uses several high-order transformations to achieve high-performance, including: blocking (for better cache reuse), loop unrolling, and scalar replacement. Because of Java's strict sequential semantics, combined with the generation of precise exceptions when an array index is out-of-bounds, these same transformations are not legal in Java.

The goal of this paper is to show that we can close the performance gap between Java and Fortran or C++. The key to achieving high-performance in Java is a new transformation that creates regions of an iteration space in which all array indices are guaranteed to be in-bounds. This has both direct and indirect benefits. First, the actual checks for array bounds can be removed in those regions. More importantly, though, because all iterations in these safe regions will execute without exceptions, many of the high-order transformations applicable to Fortran and C++ (including parallelization) can be used. In the particular case of MATMUL on a RS/6000 SP 332MHz SMP node, we have achieved fully-compliant Java performance in excess of 500 Mflops.

The rest of this paper is organized as follows. Section 2 discusses one of our methods to create safe regions, without out-of-bounds array indices. Section 3 then discusses how to apply high-order transformations to these regions and lists performance improvements obtained with Java. Section 4 shows how we can parallelize MATMUL and presents more performance results. In Section 5 we discuss some related work. In particular, we show that speculative execution is an alternative strategy to enable many of the high-order transformations. Finally, in Section 6 we conclude this paper and discuss some future work.

# 2 Optimization of Array Bounds Checking

A major impediment to optimizing Java is the requirement that exceptions be thrown precisely. An exception must be thrown for any attempt to dereference a **null** pointer or perform an out-of-bounds array access [18]. Because most references in computationally intense Java loops are to arrays or via pointers, most references have the potential to generate an exception. Because of the precise exception requirement, it is impossible to do code motion across potential exceptions, and in general it is impossible to perform many optimizations.

Our solution to this problem is to transform the program so that most computation, in programs that perform few or no invalid accesses, is in loops that are provably free of invalid accesses. Intuitively, these loops are formed by tiling the iteration space of the loop nest with regions. A region is a set of adjacent iterations in the loop nest such that either (i) all accesses in the region are provably safe, i.e. will not cause an exception to be thrown, or (ii) one or more accesses may be invalid. An iteration i is placed into a type (i) region (also called a safe region) if no reference in iteration i causes an invalid access exception. Otherwise the iteration is placed into a type (ii) region (also called an unsafe region).

To execute the two types of regions, two versions of the loop nest are formed. One version, which executes the iterations in safe regions, has no code to check for access violations. The second version, which executes the iterations in the unsafe regions, performs all access violation checks explicitly mandated by the Java VM specification. By executing the regions and the iterations within the regions in proper order, the iteration space of the loop is executed in the original execution order. However, checks are only performed in unsafe regions.

#### 2.1 Determining iterations with safe accesses

Let A[f(i)] be the reference for which the safe bounds are being found. Let i be the loop index variable of a normalized loop with stride one. We refer to this loop as loop i. We discuss the case where f(i) is a linear function of the form  $c \cdot i + b$ , where c and b are invariant within the loop, and c > 0. In [27,26], we discuss other methods for forming safe regions, and describe a variety of techniques to handle subscripted subscripts, constant subscript, general affine subscripts, and subscripts involving modulo operators. In the case of arrays of arrays, used in Java to simulate multi-dimensional arrays, we treat the access to each dimension of the array as a separate access.

Let lo(A) and up(A) be the lower and upper bounds of array A, respectively. Note that in Java programs, lo(A) will always be zero, but we specify it symbolically for generality. Let  $l_i$  and  $u_i$  be the lower and upper bounds of the iteration space of i, respectively. The safe iterations of i are defined as all iterations i such that  $f(i) \geq lo(A)$  and  $f(i) \leq up(A)$ . Solving these two inequalities for i, and intersecting with the loop iteration space, gives the range of i that will not cause access violations in reference  $A[c \cdot i + b]$ :

$$\left( \left\lceil \frac{\log(A) - b}{c} \right\rceil \le i \le \left\lfloor \frac{\operatorname{up}(A) - b}{c} \right\rfloor \right) \bigcap (l_i \le i \le u_i) \tag{1}$$

The intersection of all ranges defined by Eq. 1, for all references in loop i indexed by i, defines the lower and upper bounds of the *safe region* for i. We denote these

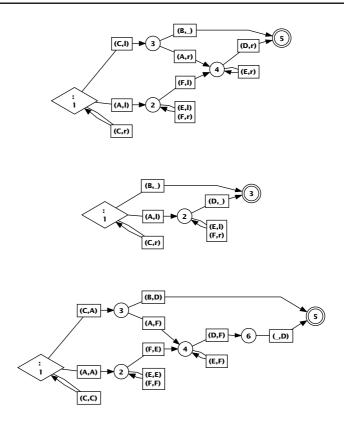

Fig. 2. Bounds optimization code generation

bounds  $l_i^s$  and  $u_i^s$ , respectively. The safe region for the loop i implicitly defines two other regions for loop i. One is the lower unsafe region,  $l_i \leq i < l_i^s$ , the other is the upper unsafe region  $u_i^s < i \leq u_i$ .

We note that if the array is known to be rectangular, then  $l_i^s$  and  $u_i^s$  need be computed only once per dimension. If the array is ragged then computing  $l_i^s$  and  $u_i^s$  for some reference requires computing it for each possible value of the other indices. That is, in a nested (i,j) loop, the values of  $l_j^s$  and  $u_j^s$  can, in general, be functions of i.

Null pointer checks can be performed on array base pointers and other pointers while computing the safe region. If a **null** is found, the safe region is made empty, and all of the iterations placed in either the lower or upper unsafe region. Details on **null** pointer issues, handling the situation where the intersection of safe regions is empty, and other boundary cases, are found in [27].

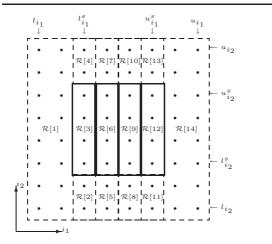

#### 2.2 Tiling the iteration space with regions

Consider a general d-dimensional rectangular loop nest, as shown in Fig. 2(a). The body of the loop is denoted by  $B(i_1, i_2, \ldots, i_d)$ . Fig. 2(b) shows the form in which the transformed code is generated. We use the full  $(l_{i_k}, u_{i_k})$  and safe  $(l_{i_k}^s, u_{i_k}^s)$  bounds of the loops to tile the iteration space. As shown in Fig. 2(b), a call is first made to a procedure regions, which computes the safe and unsafe regions that tile the iteration space of the given loop nest. The interested reader is referred to [27] for details on how these regions are computed. The  $\delta$  driver loop iterates over the regions. If a region is not safe and requires tests, the first loop, whose body,  $B_{\mathbf{test}}(i_1, i_2, \ldots, i_d)$ , contains all necessary tests, is executed.

- $\mathcal{R}[1]$ : tests in  $i_1$  and  $i_2$

- $\mathcal{R}[2], \mathcal{R}[5], \mathcal{R}[8], \mathcal{R}[11]$ : tests in  $i_2$

- $\mathcal{R}[3], \mathcal{R}[6], \mathcal{R}[9], \mathcal{R}[12]$ : no tests

- $\mathcal{R}[4], \mathcal{R}[7], \mathcal{R}[10], \mathcal{R}[13]$ : tests in  $i_2$

- $\mathcal{R}[14]$ : tests in  $i_1$  and  $i_2$

- (a) Partitioning the iteration space into regions (b) Mandatory tests in each region

**Fig. 3.** Example of iteration space for a perfectly nested two-dimensional loop.

Otherwise, the second, check-free loop nest, with body  $B_{\mathbf{notest}}(i_1, i_2, \dots, i_d)$ , is executed.

An example of such tiling is shown in Fig. 3 for a 2-dimensional iteration space. The outer  $i_1$  loop is divided into at most two unsafe regions, plus its safe regions. The inner  $i_2$  loop is, in the worst case, divided into at most three regions for each iteration of the safe region of the outer loop. In the example, there are four iterations in the outer loop safe region (*i.e.*, those iterations between  $l_{i_1}^s$  and  $u_{i_1}^s$ ).

Because each instance of the loop invoked by the driver corresponds to exactly one region as illustrated in Fig. 3, the code generation strategy facilitates code transformations. Within a region, and the corresponding loop nest, the iteration space is a contiguous subset of the original loop nest's iteration space. Thus if some iteration I' is adjacent to some iteration I in the loop nest instantiating a region, then I' is also adjacent to iteration I in the original loop nest. Stated differently, and referring to Fig. 3, the regions  $\mathcal{R}[1]$  through  $\mathcal{R}[14]$  are lexicographically ordered:

$$\mathcal{R}[1] < \mathcal{R}[2] < \mathcal{R}[3] < \mathcal{R}[4] < \dots < \mathcal{R}[14].$$

(2)

Because of this ordering, transformations within the loop nest corresponding to the safe regions are not constrained by exceptions thrown in the loop nest corresponding to an unsafe region. Furthermore, any orderings required to honor Java semantics in the presence of exceptions (thrown in iterations corresponding to unsafe regions) are enforced by the order in which regions are instantiated by the driver loop.

#### 2.3 Thread safety

Threads are an integral part of the Java language specification. In general, it is not possible to determine at compile-time if a method will be sharing data with other concurrent threads as it executes. Therefore, it is necessary that our optimization be thread safe. Thread safety of the bounds checking optimization can be ensured if the bounds of an array used during the execution of procedure regions is the same as the bounds of the array when it is accessed in the **notest** loop.

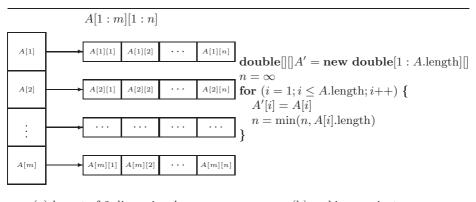

Fig. 4(a) shows the layout of a 2-dimensional Java array (as mentioned earlier, non-zero lower bounds are used for generality). Each vector (either data vector or pointer vector) contains information about its extent. The bounds of an array change when an element of a pointer vector is assigned to point to another (data or pointer) vector, whose bounds are different than what originally existed. Issues of thread safety arise when another thread is changing the bounds of an array that is accessed by a concurrently executing thread running code optimized by the transformation of this section. We denote the thread changing the array bound as  $T_c$ , and the thread executing optimized code that accesses array elements as  $T_o$ , and give a worst case scenario. We stress that while asynchronously changing array extents may be poor programming practice, it is legal Java.

- (a) layout of 2-dimensional array

- (b) making a private copy

Fig. 4. Thread-safety issues are handled by privatizing data.

First,  $T_o$  executes regions, and computes  $l_i^s$  and  $u_i^s$  for the loop index i. Thread  $T_c$  then changes the extent of one vector of floating point numbers (v) to be shorter (so much shorter that  $u_i^s$  is no longer valid) by replacing it with v'. The storage after v' happens to be filled with values that are illegal floating point numbers. Next, during the execution of the **notest** loop, the value of the subscript function f(i) exceeds the length of v', and a value that is an illegal floating point number is fetched. An operation is executed on the value, and the

program generates an incorrect result (e.g., NaN). Two non-compliant events have occurred: (i) an out-of-bounds access was performed and no exception was thrown, and (ii) the result of the optimized program does not correspond to a valid execution of the original program.

Fortunately, the Java memory model provides a solution to this problem. Java allows keeping copies of shared (or main memory) values in thread-private memory (or working memory) between synchronization points. To guarantee thread safety, we keep the vectors of pointers in private memory. Thus, referring to Fig. 4(a), (the values of) the A[1:m] vector will be kept in private memory during computation. These private values are then used by procedure regions, and the **test** and **notest** loops. Thus, any races and asynchronous changes in the size of the array will occur before the computation of  $l_i^s$  and  $u_i^s$ , and these values will be consistent throughout the execution of the modified code.

We show how to implement the privatization by copying array A[1:m] into a private array A'[1:m] in Fig. 4(b). While copying we can find the minimum extent of a row of A. In computing the safe bounds, A can be treated as rectangular, with this minimum extent as its second-axis extent. (In other words, this is the number of columns of A.) Matrix multiplication of  $n \times n$  matrices is an  $O(n^3)$  operation. The cost of privatizing and verifying the extents of one of the matrices is only O(n). This is certainly insignificant for n = 500. We discuss some approaches to deal with very small n or less intensive computations in Section 5.

#### 2.4 An alternate approach

Finally, we discuss here an alternative to this regions approach. A normal execution of a method such as matmul in Fig. 1 is expected to generate no exceptions. With current programming styles, an execution that causes an exception is most likely a misuse and it is not really important to optimize. Optimization of the normal case (no exceptions) can be achieved by a simple set of range tests before the execution of a loop nest. Let a loop nest have a reference of the form  $A[\sigma]$  in its body. Let  $\min(\sigma)$  and  $\max(\sigma)$  be the smallest and largest values, respectively, that  $\sigma$  evaluates to during execution of the loop nest. A simple evaluation of  $(\min(\sigma) \geq \log(A)) \wedge (\max(\sigma) \leq \sup(A))$  can tell if  $A[\sigma]$  is guaranteed to always be safe or not. In the particular case of MATMUL, the triple-nested loop of Fig. 1 can be transformed to the following two-version code:

```

\begin{array}{l} \textbf{if} \; ( \; (m \leq \mathbf{rows}(C)) \land (p \leq \mathbf{cols}(C)) \land \\ \; (m \leq \mathbf{rows}(A)) \land (n \leq \mathbf{cols}(A)) \land \\ \; (n \leq \mathbf{rows}(B)) \land (p \leq \mathbf{cols}(B)) \; \; ) \; \{ \\ \textbf{notest} \; \text{version of loop-nest} \\ \textbf{else} \; \{ \\ \; \textbf{test} \; \text{version of loop-nest} \\ \} \end{array}

```

where  $\mathbf{rows}(A)$  and  $\mathbf{cols}(A)$  denote the number of rows and columns of matrix A, respectively.

In loop nests where there are no exceptions (*i.e.*, all iterations of a loop are in a single safe region) the two-version code is, for all practical purposes, equivalent to the regions method. In this situation we have verified that the performance of the two methods (measured using MATMUL) is within our experimental error. Because a hand-implementation of the two-version method is simpler, we have used that approach in our experiments.

If there are bounds exceptions in the loop nest, the difference in performance between the two can be dramatic. For example, if the two version method was used, a single exception in some iteration of the outer loop would force the entire loop to run with checks and without optimizations. This is the case even if the exception is expected and cleanly handled by a **try-catch** clause. Using the regions based methods, the majority of the iteration space can still execute fully optimized. In [29], a programming style that uses array bounds exceptions as loop termination conditions is advanced. Regardless of how offensive this style may appear to a Fortran or C++ programmer, the loop termination condition is apparently simpler. Therefore, it is likely that this and related styles will enjoy some degree of popularity. With this style of programming, the versioning method will see no benefit from optimizations that require safe regions. In contrast, the regions based method will allow code with the best possible level of optimization to be selected dynamically (by the regions driver loop).

## 3 Optimizations

In this section, we describe the impact of various program transformations on the performance of the MATMUL program executing on a single processor. For completeness, we also analyze another program, MICROSTRIP, which does not have  $O(n^3)$  behavior. This study was performed using the IBM HPCJ compiler for the POWER family of architectures [33], which converts the Java bytecode into native code of the target machine. The kernel of the MATMUL program is shown in Fig. 1. The transformations that we applied to this program are described below.

#### 3.1 Program Transformations

The first program transformation reduces the overhead of checking for out-of-bounds array access violations, as described in Section 2. We generate two versions of the loop nest, one in which bounds checking computations are performed for each array reference, and the other in which no such computations are needed. A correctly written program is expected to execute the loop nest without bounds checking. This transformation not only reduces the overhead of array bounds checking, but also creates program regions that are provably free from exceptions. Those regions can now be transformed using standard loop transformation techniques [37,3,35,30] without violating Java semantics.

The next transformation on the program is to tile (block) the loop nest in the exception-free region, to improve the cache-performance by promoting greater

reuse of data [36,30]. Tiling requires both strip-mining, which does not change the order of computation, and loop-interchange, which does change the order of computation. Loop-interchange (and tiling) can be legally performed only on that part of a Java program in which no exception may be thrown. Based on the existing algorithm in the IBM XLF compiler [30] to select the loop blocking parameters (which uses estimates of the number of distinct cache lines touched by the computation [15]), we choose strip size of 40 for each of the i, j, and k loops in the PowerPC 604e and strip size of 120 for the same loops in the PowerR2.

Following loop tiling, we perform loop-unrolling [30] to increase the size of the loop body. This enables the backend to generate a better schedule that exploits the instruction-level parallelism. It also enhances data reuse within registers. We perform outer loop-unrolling, where both the i and the j loops are unrolled by a factor of 4 each.

The next program version uses scalar replacement [8,30], where references to the array being written, C, are replaced by references to scalar temporary variables in the innermost loop. Additional statements are used to load the temporaries from the array at the beginning of the loop iteration and to store them back at the end. It is well-known that scalar replacement enables the compiler backend to improve register-allocation for the code, as most backends are able to disambiguate scalar references more effectively.

Finally, to determine the performance benefits from the **looseNumerics** extension to Java [17] (described in Section 5), which allows the use of extended-precision (greater than 32- and 64-bit) arithmetic, we modified the compiler options that are passed on by the Java compiler to the backend. We turned on the option that allows the backend to use the fma (fused multiply-add) instruction. The fma instruction in the POWER family of architectures, fma a, b, c, x, computes x = a + b \* c.

The programs were compiled using the -0 option of the IBM HPCJ compiler, and with the -qarch and -qtune options set to turn on code tuning for the respective PowerPC and POWER2 architectures.

#### 3.2 Experimental Results

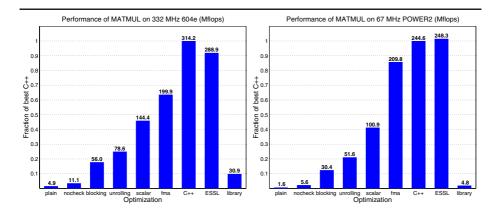

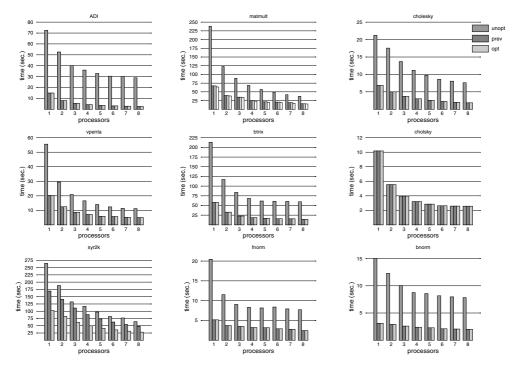

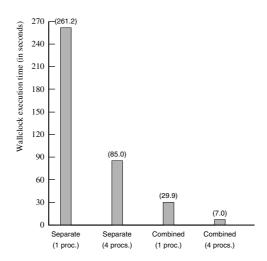

Fig. 5 shows the performance of different versions of the MATMUL program on a PowerPC 604e and a Power2 workstation, expressed as a fraction of the performance obtained for the best version written in C++. On the PowerPC, the base-line Java version achieves a performance of only 4.9 MFlops. After the transformation to create a safe region with no array bounds checking, the performance improves to 11.1 MFlops. The indirect impact of that transformation is even more significant. The application of tiling, which is enabled by that transformation, followed by other loop transformations described above, steadily improves the performance of the program. The final Java-compliant optimized program achieves a performance of 144.4 MFlops on the PowerPC, while the version which exploits the proposed **looseNumerics** Java extension (by using fma instructions) achieves 199.9 MFlops. This is 63.6% of the performance of

Fig. 5. Summary of results for MATMUL. (Mflop numbers at the top of each bar.)

the equivalent C++ version with identical loop transformations, and 69.2% of the hand-tuned ESSL version.

On the Power2, the impact of these transformations is even more dramatic. The base-line Java program achieves 1.6 MFlops, whereas the optimized version with fma instructions achieves a performance of 209.8 MFlops, for an improvement by a factor of 131. The fully optimized Java program achieves 85.8% of the performance of the corresponding C++ version, and 84.5% of the ESSL performance.

For both machines, we also show the performance of the best Java version (with fma instructions) where only the transformation to create safe, exception-free, regions is not performed (these are the "library" bars). It would not be legal for a compiler to derive such a version from the given base-line program, as it has different semantics under Java when exceptions are possible. However, this measurement helps quantify the overhead of array bounds checking in an otherwise tuned (BLAS-3 style [14]) matrix-multiply routine. It can be seen that the performance of this version is quite poor on both the machines: 30.9 MFlops on a PowerPC and 4.8 MFlops on a PowerP2.

In summary, the transformation to create exception-free regions in the MATMUL program has a large positive impact on the performance of the program, in two ways. First, it eliminates the actual overhead of bounds checking (which is more significant on the higher-performance version of the program). Second, it enables other loop transformations, which can be performed automatically by a compiler.

#### 3.3 The MICROSTRIP benchmark

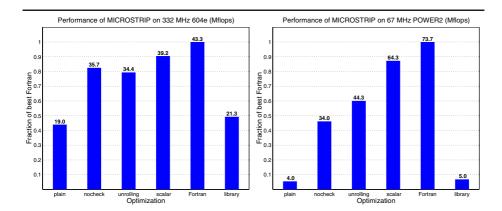

We use the MICROSTRIP benchmark to demonstrate that bounds checking optimization and the enabled transformations can also improve the performance of non- $O(n^3)$  computation. This benchmark solves the Poisson equation for the

potential field in a dielectric. It uses an iterative solver. Each iteration involves two relaxation steps and the computation of an error value. Source code for these operations is shown in Fig. 6. These are both  $O(n^2)$  computations.

Fig. 6. Main computations in MICROSTRIP.

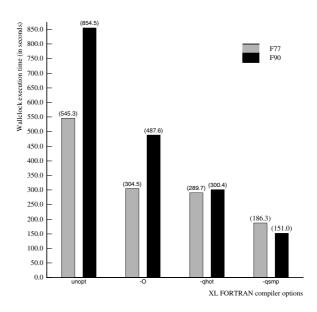

The results for MICROSTRIP on both the PowerPC 604e and the POWER2 are shown in Fig. 7 (there is no ESSL version for this benchmark). Also, it does not benefit from the fma instruction (none are generated by the compiler) and that bar is absent as well. The reference performance is that obtained by the Fortran compiler with the highest level of optimization. The benefit of optimizing the checks for Java is more evident on the POWER2, where the performance jumps from 4.0 to 34.0 Mflops. Further optimizing the code with loop unrolling (of both the i and j loops of Fig. 6(a)) and scalar replacement brings Java performance to 87% of peak Fortran performance on the POWER2.

The performance of  $O(n^2)$  matrix computations is often constrained by memory bandwidth, rather than processor speed. Therefore, we do not see great improvements in the PowerPC 604e, which has lower memory bandwidth than the Power2. Nevertheless, optimizing the checks nearly doubles the performance of the Java version of MICROSTRIP. Additional optimizations bring it to 90% of Fortran performance. Again, in both plots we indicate by "library" the performance of the best Java version without checks optimization.

#### 4 Parallelization

The final step in optimizing the performance of MATMUL is parallelization. It is not legal to directly parallelize the (i,j,k) loop nest of the Java version of MATMUL. Because exceptions can be thrown in any iteration of the loop nest, we have to guarantee that the values of C[i][j] are modified in the sequential order of the iterations. Fortunately, the transformation of Section 2 creates regions that are exception-free. The same transformation that enabled blocking, unrolling, and the other optimizations of Section 3 also enables parallelization.

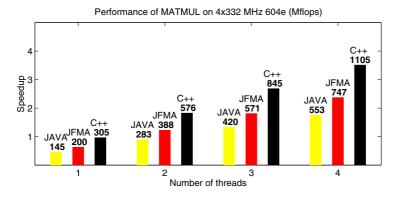

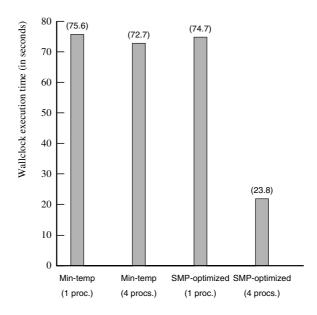

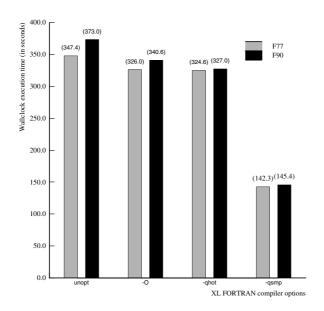

Fig. 8 presents our results from parallelization of MATMUL(see [28] for details). We show the performance of three versions of MATMUL for different number of threads: (i) a version that conforms to current Java semantics (identified by

**Fig. 7.** Summary of results for MICROSTRIP. (Mflop numbers at the top of each bar.)

JAVA), (ii) a version with Java using the fma instructions (identified by JFMA), and (iii) a C++ version (identified by C++). The numbers at the top of the bars are the absolute Mflops achieved by each version. The speedup in each case is computed with respect to the best sequential case, 314 Mflops. The peak ESSL performance was 1183 Mflops.

Fig. 8. Performance results comparing Java, Java with fmas, and C++.

Overall, we observe good scaling with the number of threads in all three versions: JAVA, JFMA, and C++. The C++ version achieves more than 90% of the peak ESSL performance. The version of Java with fma instructions, JFMA,

achieves almost 2/3 of the peak ESSL performance. While this is still 30% less than the C++ version, it is a very respectable result. Even the strict Java version, JAVA, achieved more than 500 Mflops. This represents a more than 100-fold improvement in performance over our starting point!

#### 5 Related Work

Examples of projects using Java for substantial numerical computing are described in [2,6,9,31]. In some cases, results have been positive despite the performance disadvantages of Java. As shown in [6], for some computations and certain machine configurations, current Java implementations can achieve within 50% of C performance. We note however, that the best performance reported in [6] for matrix multiplication in Java is only 50 Mflops.

There are four main approaches in the literature to optimizing array bounds checks: (i) the use of static data-flow analysis information to determine that a test is unnecessary [11,21,12,13,32], (ii) the use of data-flow information and symbolic analysis at compile time to reduce the dynamic number of tests remaining in the program [23,20,1,19,24], (iii) the regions based approach discussed in this paper and more generally in [26,27], and (iv) speculative methods discussed in [26].

Work in the first group uses data-flow information to prove at compile time that an array bounds violation cannot occur at run-time, and therefore that the test for the violation is unnecessary. Using the terms of our discussion, the goal of this work is to identify loops that are safe regions. In contrast, the goal of our work is to transform loops in order to *create* safe regions.

Work in the second group attempts to reduce the dynamic and static number of bounds tests. It also attempts to reduce the overhead induced by a test even if it cannot be eliminated. This is done (i) by hoisting tests out of loops when possible [24] and (ii) by also determining that a test is covered by another test [23,20,1,19] and can be eliminated.

Neither of these optimizations are usable with Java in general because the Java semantics requiring precise exceptions make the hoisting and reordering of tests illegal in many situations. Also, when an access violation exception is caught by a **try** block in the loop body, the loop should not be terminated (as would occur when hoisting tests).

The work in the third and fourth groups differs from what is discussed here in the generality of discussion, and in the experiments performed. Specifically, in [26] no benchmarking was performed. In [27] measurements compared the performance of programs with all checks, no checks, and our transformations. The more important effects of the transformation in enabling other optimizations was neither discussed in any detail, nor measured.

We emphasize that creating safe regions has the important effect of enabling an entire set of powerful optimization techniques. These techniques are constrained in Java by the requirement of precise exceptions. An alternative approach that enables this optimizations even in presence of (potential) exceptions is *speculative execution* [26]. A fully transformed and optimized version of a

loop nest (or code fragment in general) can be generated and executed speculatively. If an access violation is detected, then the computation is rolled-back and restarted in strict order. This approach is analogous to speculative execution to explore parallelism in the presence of (potential) data dependences. Note that some mechanism to detect violations is necessary, so this approach does not get the benefit of eliminating the actual tests.

Several other projects have looked at aggressively optimizing Java. In [5] and [4], the **javar** and **javab** projects are described. These projects are closely related, with **javar** compiling Java source code and **javab** compiling byte code. The **javar** restructurer supports user specified parallelism, and the **javab** performs automatic parallelization. In [7], a project begun at the JavaSoft division of Sun Microsystems and its follow-on at Rice University are outlined. The work was aimed at a dynamic (or just-in-time) compilation system, and focused on local scalar optimizations. Hand compilations using a technique called object inlining achieved up to a 7-fold speedup on an Oopack routine (an object-oriented version of Linpack). The work of both of these projects are complementary to our work, and show the gains that can be made in Java performance.

Several groups have put forth proposals for altering the Java floating point semantics to allow greater freedom in scheduling floating point operations and exploiting floating point hardware. In [17], James Gosling describes a looseNumerics and idealizedNumerics class and method modifiers. The looseNumerics modifier allows a class or method to return floating point results with more precision than allowed by the Java standard. This enables the use of the fma operation on the IBM POWER and PowerPC architectures. For Intel x86 processors, it allows intermediate and local variables to be kept in full 80-bit precision. As seen in Section 3.2, enabling the fma operation can have a dramatic effect on performance. Similar benefits should accrue to programs compiled for the x86 processors. The idealizedNumerics modifier would allow floating point operations to be reordered as if they were associative, and would, for example, allow parallelization of the inner loop recurrence in the matrix multiply.

Sun has submitted for public review a change to the Java programming language [25,34] that allows extended precision in intermediate results. This proposal is similar to the **looseNumerics** proposal described above, and would allow the use of the fma operation. The Java Grande Forum, which is looking into the use of Java for high performance computing, is also working on proposals (see [16]) to relax Java floating point semantics.

Finally, various researchers have studied the benefit of adding rectangular, multidimensional arrays to Java. True multidimensional arrays have several advantages over Java arrays-of-arrays, such as: better data locality due to contiguous data allocation, simpler address computation of array elements, and better aliasing disambiguation. Specifically, in the context of our work, true multidimensional arrays offer the added advantages of simpler bounds checking optimization due to their fixed shapes, and reduced overhead of privatizing the array for thread-safety while performing the bounds checking optimization.

#### 6 Conclusions

Eliminating and/or reducing the cost of verifying array references for validity is a key factor for achieving high-performance in Java for technical computing. The method we presented in this paper partitions the iteration space of a loop-nest into regions with different access violation characteristics. For technical computing, we expect most or all of the work to be performed in safe and exception-free regions. The benefit of creating safe regions is two-fold: (i) code to explicitly check for valid references is unnecessary in those regions and (ii) operation-reordering optimizations are allowed.

By applying high-order loop transformations (available today in the IBM XLF compiler) we have achieved single-processor Java performance in MATMUL that is within 65–85% of the best library and Fortran/C++ versions. We want to stress the fact that there are no fundamental reasons for the Java code not to achieve the same performance as C++ in the serial and parallel versions of MATMUL. The current differences are due to differences in the compilers, which result in different instructions schedules. As part of our future work, we want to investigate the causes of these differences and to provide the necessary fixes. Furthermore, in the MICROSTRIP application, we achieved 87–90% of the performance of a Fortran version of the code. This shows that the performance gains achieved with MATMUL are also attainable on  $O(n^2)$  computations.

The safe regions also open up the possibility of automatic parallelization of Java codes. Automatic parallelization is being developed at IBM within the context of the *Toronto Portable Optimizer* (TPO) framework. This framework operates at an intermediate language level, and it is equally applicable to Fortran, C, C++, and Java. Parallelization of MATMUL yielded almost linear speedup for Java, achieving 750 Mflops on  $4 \times 332$  MHz PowerPC 604e machine. We are looking forward to soon smashing the 1 Gflop barrier!

# Acknowledgments

The authors wish to thank Rick Lawrence and Marc Snir for fruitful technical discussions, and for strongly supporting our research.

#### References

- 1. J.M. Asuru. Optimization of array subscript range checks. ACM Letters on Programming Languages and Systems, 1(2):109–118, June 1992. 13, 13

- C. A. Atwood, R. P. Garg, and D. DeRyke. A prototype computational fluid dynamics case study in Java. *Concurrency, Pract. Exp. (UK)*, 9(11):1311–18, November 1997. Java for Computational Science and Engineering - Simulation and Modeling II Las Vegas, NV, USA 21 June 1997. 13

- U. Banerjee. Unimodular transformations of double loops. In Proc. Third Workshop on Programming Languages and Compilers for Parallel Computing, Irvine, California, August 1990.

- 4. A. Bik and D. Gannon. **javab** manual (version 1.0 BETA. In *ACM 1998 Workshop on Java for High-Performance Network Computing*. ACM SIGPLAN, 1998. Available at URL http://www.cs.ucsb.edu/conferences/java98. 14

- A. Bik, J. Villacis, and D. Gannon. javar: A prototype Java restructuring compiler. Concurrency, Pract. Exp. (UK), 9(11):1181–91, November 1997. Java for Computational Science and Engineering Simulation and Modeling II Las Vegas, NV, USA 21 June 1997. 14

- R. F. Boisvert, J. J. Dongarra, R. Pozo, K. A. Remington, and G. W. Stewart. Developing numerical libraries in Java. In ACM 1998 Workshop on Java for High-Performance Network Computing. ACM SIGPLAN, 1998. Available at http://www.cs.ucsb.edu/conferences/java98. 13, 13, 13

- Z. Budimlic and K. Kennedy. Optimizing Java: Theory and practice. Concurrency, Pract. Exp. (UK), 9(11):445–63, November 1997. Java for Computational Science and Engineering - Simulation and Modeling II Las Vegas, NV, USA 21 June 1997.

14

- 8. D. Callahan, S. Carr, and K. Kennedy. Improving register allocation for subscripted variables. In *Proc. ACM SIGPLAN '90 Conference on Programming Language Design and Implementation*, White Plains, NY, June 1990. 9

- H. Casanova, J. Dongarra, and D. M. Doolin. Java access to numerical libaries. Concurrency, Pract. Exp. (UK), 9(11):1279–91, November 1997. Java for Computational Science and Engineering - Simulation and Modeling II Las Vegas, NV, USA 21 June 1997. 13

- IBM Corporation. IBM High Performance Compiler for Java, 1997. Available for download at http://www.alphaWorks.ibm.com/formula.

- 11. P. Cousot and R. Cousot. Abstract interpretation: A unified lattice model for static analysis of programs by construction or approximation of fixpoints. In *Conference Record of the 4'th ACM Symposium on Principles of Programming Languages*, pages 238–252, January 1977. 13

- P. Cousot and N. Halbwachs. Automatic discovery of linear restraints among variables of a program. In Conference Record of the 5'th ACM Symposium on Principles of Programming Languages, pages 84–96, January 1978.

- P. Cousot and N. Halbwachs. Automatic proofs of the absence of common runtime errors. In Conference Record of the 5'th ACM Symposium on Principles of Programming Languages, pages 105–118, January 1978.

- J.J. Dongarra, I.S. Duff, D.C. Sorensen, and H.A. van der Vorst. Solving Linear Systems on Vector and Shared Memory Computers. Society for Industrial and Applied Mathematics, 1991. 10

- J. Ferrante, V. Sarkar, and W. Thrash. On estimating and enhancing cache effectiveness. In Proc. Fourth Workshop on Programming Languages and Compilers for Parallel Computing, August 1991.

- 16. Java Grande Forum. Issues in numerical computing with Java. Document available at URL http://math.nist.gov/javanumerics/issues.html, March 1998. 14

- James Gosling. The evolution of numerical computing in Java. Document available at Web-page http://java.sun.com/people/jag/FP.html. Sun Microsystems. 9, 14

- 18. James Gosling, Bill Joy, and Guy Steele. The Java (TM) Language Specification. Addison-Wesley, 1996. 3

- R. Gupta. A fresh look at optimizing array bounds checking. In Proceedings of the ACM SIGPLAN '90 Conference on Programming Language Design and Implementation, pages 272–282, June 1990. 13, 13

- R. Gupta. Optimizing array bound checks using flow analysis. ACM Letters on Programming Languages and Systems, 2(1-4):135–150, March–December 1993. 13,

- 21. W.H. Harrison. Compiler analysis for the value ranges for variables. *IEEE Transactions on Software Engineering*, SE3(3):243–250, May 1977. 13

- 22. International Business Machines Corporation. *IBM Engineering and Scientific Subroutine Library for AIX Guide and Reference*, December 1997. 2

- 23. P. Kolte and M. Wolfe. Elimination of redundant array subscript range checks. In *Proceedings of the ACM SIGPLAN '95 Conference on Programming Language Design and Implementation*, pages 270–278, Jun 1995. 13, 13

- V. Markstein, J. Cocke, and P. Markstein. Elimination of redundant array subscript range checks. In Proceedings of the ACM SIGPLAN '82 Conference on Programming Language Design and Implementation, pages 114–119, June 1982.

13, 13

- Sun Microsystems. Sun proposes modification to Java programming languages's floating point specification. http://www.sun.com/smi/Press/sunflash/9803/ sunflash.980324.17.html, 1998. 14

- S. P. Midkiff, J. E. Moreira, and M. Gupta. Method for optimizing array bounds checks in programs. Patent pending, IBM Docket #YO-998-052, filed with U. S. Patent Office, April 24th, 1998. 3, 13, 13, 13

- 27. S.P. Midkiff, J.E. Moreira, and M. Snir. Optimizing bounds checking in java programs. *IBM Systems Journal*, 37(3):409–453, August 1998. 3, 4, 4, 13, 13

- J. E. Moreira, S. P. Midkiff, and M. Gupta. From flop to megaflops: Java for technical computing, 1998. Submitted to ACM TOPLAS, IBM Research Report 21166. 11

- D. Orchard. Better peformance with exceptions in Java. Byte, pages 53–54, March 1998. In the Core Programming feature.

- V. Sarkar. Automatic selection of high-order transformations in the IBM XL Fortran compilers. IBM Journal of Research and Development, 41(3), May 1997.

9, 9, 9, 9

- 31. M. Schwab and J. Schroeder. Algebraic java classes for numerical optimization. In *ACM 1998 Workshop on Java for High-Performance Network Computing*. ACM SIGPLAN, 1998. Available at http://www.cs.ucsb.edu/conferences/java98. 13

- B. Schwarz, W. Kirchgassner, and R. Landwehr. An optimizer for Ada design, experience and results. In Proceedings of the ACM SIGPLAN '88 Conference on Programming Language Design and Implementation, pages 175–185, June 1988.

- 33. V. Seshadri. IBM high performance compiler for Java. AIXpert Magazine, September 1997. Electronic publication available at URL http://www.developer.ibm.com/library/aixpert. 8

- 34. Proposal for extension of java floating point in jdk 1.2. http://java.sun.com/feedback/fp.html, 1998. 14

- 35. M. E. Wolf and M. S. Lam. A loop transformation theory and an algorithm to maximize parallelism. *IEEE Transactions on Parallel and Distributed Systems*, 2(4):452–471, October 1991. 8

- M. J. Wolfe. Iteration space tiling for memory hierarchies. In Proc. 3rd SIAM Conference on Parallel Processing for Scientific Computing, pages 357–361, Philadelphia, PA, 1987.

- 37. M. J. Wolfe. Optimizing Supercompilers for Supercomputers. The MIT Press, 1989.

# Considerations in HPJava Language Design and Implementation

Guansong Zhang, Bryan Carpenter, Geoffrey Fox, Xinying Li, and Yuhong Wen

NPAC at Syracuse University Syracuse, NY 13244, USA {dbc,zgs,gcf,lxm,xli,wen}@npac.syr.edu

**Abstract.** This paper discusses some design and implementation issues in the *HPJava* language. The language is briefly reviewed, then the class library that forms the foundation of the translation scheme is described. Through example codes, we illustrate how HPJava source codes can be translated straightforwardly to ordinary SPMD Java programs calling this library. This is followed by a discussion of the rationale for introducing the language in the first place, and of how various language features have been designed to facilitate efficient implementation.

#### 1 Introduction

*HPJava* is a programming language extended from Java to support parallel programming, especially (but not exclusively) data parallel programming on message passing and distributed memory systems, from multi-processor systems to workstation clusters.

Although it has a close relationship with HPF [5], the design of HPJava does not inherit the HPF programming model. Instead the language introduces a high-level structured SPMD programming style—the *HPspmd* model. A program written in this kind of language explicitly coordinates well-defined process groups. These cooperate in a loosely synchronous manner, sharing logical threads of control. As in a conventional distributed-memory SPMD program, only a process owning a data item such as an array element is allowed to access the item directly. The language provides special constructs that allow programmers to meet this constraint conveniently.

Besides the normal variables of the sequential base language, the language model introduces classes of global variables that are stored collectively across process groups. Primarily, these are *distributed arrays*. They provide a global name space in the form of globally subscripted arrays, with assorted distribution patterns. This helps to relieve programmers of error-prone activities such as the local-to-global, global-to-local subscript translations which occur in data parallel applications.

In addition to special data types the language provides special constructs to facilitate both data parallel and task parallel programming. Through these constructs, different processors can either work simultaneously on globally addressed data, or independently execute complex procedures on locally held data. The conversion between these phases is seamless.

In the traditional SPMD mold, the language itself does not provide implicit data movement semantics. This greatly simplifies the task of the compiler, and should encourage programmers to use algorithms that exploit locality. Data on remote processors is accessed exclusively through explicit library calls. In particular, the initial HPJava implementation relies on a library of collective communication routines originally developed as part of an HPF runtime library. Other distributed-array-oriented communication libraries may be bound to the language later. Due to the explicit SPMD programming model, low level MPI communication is always available as a fall-back. The language itself only provides basic concepts to organize data arrays and process groups. Different communication patterns are implemented as library functions. This allows the possibility that if a new communication pattern is needed, it is relatively easily integrated through new libraries.

The preceding paragraphs attempt to characterize a language independent programming style. This report only briefly sketches the HPJava language. For further details, please refer to [2,15]. Here we will discuss in more depth some issues in the language design and implementation. With the pros and cons explained, the language can be better understood and appreciated.

Since it is easier to comment on the language design with some knowledge of its implementation, this document is organized as follows: section 2 briefly reviews the HPJava language extensions; section 3 outlines a simple but complete implementation scheme for the language; section 4 explains the language design issues based on its implementation; finally, the expected performance and test results are given.

#### 2 Overview of HPJava

Java already provides parallelism through threads. But that model of parallelism can only be easily exploited on shared memory computers. HPJava is targetted at distributed memory parallel computers (most likely, networks of PCs and workstations).

HPJava extends Java with class libraries and some additional syntax for dealing with distributed arrays. Some or all of the dimensions of a these arrays can be declared as distributed ranges. A distributed range defines a range of integer subscripts, and specifies how they are mapped into a process grid dimension. It is represented by an object of base class Range. Process grids—equivalent to processor arrangements in HPF—are described by suitable classes. A base class Group describes a general group of processes and has subclasses Procs1, Procs2, ..., representing one-dimensional process grids, two-dimensional pro-

cess grids, and so on. The inquiry function dim returns an object describing a particular dimension of a grid. In the example

```

Procs2 p = new Procs2(3, 2);

Range x = new BlockRange(100, p.dim(0));

Range y = new BlockRange(200, p.dim(1));

float [[,]] a = new float [[x, y]] on p;

```

a is created as a  $100 \times 200$  array, block-distributed over the 6 processes in p. The Range subclass BlockRange describes a simple block-distributed range of subscripts, analogous to BLOCK distribution format in HPF. The arguments of the BlockRange constructor are the extent of the range and an object defining the process grid dimension over which the range is distributed.

In HPJava the type-signatures and constructors of distributed arrays use double brackets to distinguish them from ordinary Java arrays. Selected dimensions of a distributed array may have a collapsed (sequential) ranges rather than a distributed ranges: the corresponding slots in the type signature of the array should include a \* symbol. In general the constructor of the distributed array is followed by an on clause, specifying the process group over which the array is distributed. (If this is omitted the group defaults to the APG, see below.) Distributed ranges of the array must be distributed over distinct dimensions of this group.

A standard library, Adlib, provides functions for manipulating distributed arrays, including functions closely analogous to the array transformational intrinsic functions of Fortran 90. For example:

```

float [[,]] b = new float [[x, y]] on p;

Adlib.shift(b, a, -1, 0, CYCL);

float g = Adlib.sum(b);

```

The shift operation with shift-mode CYCL executes a cyclic shift on the data in its second argument, copying the result to its first argument. The sum operation simply adds all elements of its argument array. In general these functions imply inter-processor communication.

Often in SPMD programming it is necessary to restrict execution of a block of code to processors in a particular group p. Our language provides a short way of writing this construct

The language incorporates a formal idea of an active process group (APG). At any point of execution some group is singled out as the APG. An on(p) construct specifically changes its value to p. On exit from the construct, the APG is restored to its value on entry.

Subscripting operations on distributed arrays are subject to some restrictions that ensure data accesses are local. An array access such as

```

a [17, 23] = 13;

```

is forbidden because typical processes do not hold the specified element. The idea of a *location* is introduced. A location can be viewed as an abstract element, or "slot", of a distributed range. The syntax x [n] stands for location n in range x. In simple array subscripting operations, distributed dimensions of arrays can only be subscripted using locations (not integer subscripts). These must be locations in the appropriate range of the array. Moreover, locations appearing in simple subscripting operations must be *named locations*, and named locations can only be scoped by at and overall constructs.

The *at* construct is analogous to *on*, except that its body is executed only on processes that hold the specified location. The array access above can be safely written as:

```

at(i = x [17])

at(j = y [23])

a [i, j] = 13;

```

Any location is mapped to a particular slice of a process grid. The body of the at construct only executes on processes that hold the location specified in its header.

The last distributed control construct in the language is called overall. It implements a distributed parallel loop, and is parametrized by a range. Like at, the header of this construct scopes a named location. In this case the location can be regarded as a parallel loop index.

```

float [[,]] a = new float [[x, y]], b = new float [[x, y]] ;

overall(i = x)

overall(j = y)

a [i, j] = 2 * b [i, j] ;

```

The body of an *overall* construct executes, conceptually in parallel, for every location in the range of its index. An individual "iteration" executes on just those processors holding the location associated with the iteration. Because of the rules about use of subscripts, the body of an *overall* can usually only combine elements of arrays that have some simple alignment relation relative to one another. The <code>idx</code> member of <code>Range</code> can be used in parallel updates to yield expressions that depend on global index values.

Other important features of the language include Fortran-90-style regular array sections (section construction operations look similar to simple subscripting operations, but are distinguished by use of double brackets), an associated idea of subranges, and subgroups, which can be used to represent the restricted APG inside at and overall constructs.

The language extensions are most directly targetted at data parallelism. But an HPJava program is implicitly an SPMD Java program, and task parallelism is available by default. A structured way to write a task parallel program is to write an overall construct parametrized by a process dimension (which is a particular kind of range). The body of the loop executes once in each process. The body can execute one or more "tasks" of arbitrary complexity. Task parallel programming with distributed arrays can be facilitated by extending the standard library with one-sided communication operations to access remote patches of the arrays, and we are investigating integration of software from the PNNL Global Array Toolset [8] in this connection.

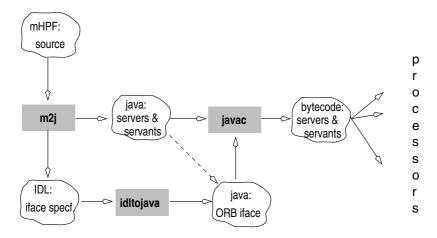

#### 3 Translation scheme

The initial HPJava compiler is implemented as a source-to-source translator converting an HPJava program to a Java node program, with calls to runtime functions. The runtime system is built on the NPAC PCRC runtime library [3], which has a kernel implemented in C++ and a Java interface implemented in Java and C++.

#### 3.1 Java packages for HPspmd programming

The current runtime interface for HPJava is called *adJava*. It consists of two Java packages. The first is the HPspmd runtime proper. It includes the classes needed to translate language constructs. The second package provides communication and some simple I/O functions. These two packages will be outlined in this section.

The classes in the first package include an environment class, distributed array "container classes", and related classes describing process groups and index ranges. The environment class SpmdEnv provides functions to initialize and finalize the underlying communication library (currently MPI). Constructors call native functions to prepare the lower level communication package. An important field, apg, defines the group of processes that is cooperating in "loose synchrony" at the current point of execution.

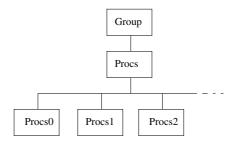

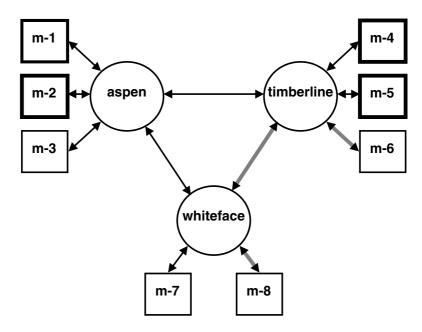

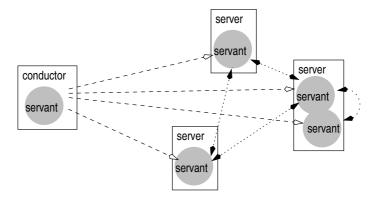

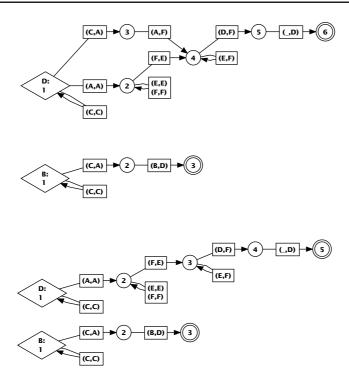

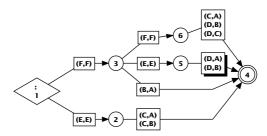

The other classes in this package correspond directly to HPJava built-in classes. The first hierarchy is based on Group. A group, or process group, defines some subset of the processes executing the SPMD program. Groups have two important roles in HPJava. First they are used to describe how program variables such as arrays are distributed or replicated across the process pool. Secondly they are used to specify which subset of processes execute a particular code fragment. Important members of adJava Group class include the pair on(), no() used to translate the on construct. The most common way to create a group object is through the constructor for one of the subclasses representing a process grid. The subclass Procs represents a grid of processes and carries information on process dimensions: in particular an inquiry function dim(r) returns a range object describing the r-th process dimension. Procs is further subclassed by Procs0, Procs1, Procs2, ... which provide simpler constructors for fixed dimensionality process grids. The class hierarchy of groups and process grids is shown in figure 1.

Fig. 1. The HPJava Group hierarchy

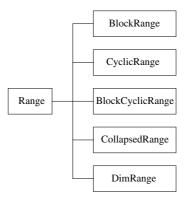

The second hierarchy in the package is based on Range. A range is a map from the integer interval  $0, \ldots, n-1$  into some process dimension (ie, some dimension of a process grid). Ranges are used to parametrize distributed arrays and the *overall* distributed loop. The most common way to create a range object

Fig. 2. The HPJava Range hierarchy

is to use the constructor for one of the subclasses representing ranges with specific distribution formats. The current class hierarchy is given in figure 2. Simple block distribution format is implemented by BlockRange, while CyclicRange and BlockCyclicRange represent other standard distribution formats of HPF. The subclass CollapsedRange represents a sequential (undistributed range). Finally, DimRange represents the range of coordinates of a process dimension itself—just one element is mapped to each process.

The related adJava class Location represents an individual location in a particular distributed range. Important members of the adJava Range class include the function location(i) which returns the *i*th location in a range and its inverse, idx(1), which returns the global subscript associated with a given

location. Important members of the Location class include at() and ta(), used in the implementation of the HPJava that at construct.

Finally in this package we have the rather complex hierarchy of classes representing distributed arrays. HPJava global arrays declared using [[]] are represented by Java objects belonging to classes such as:

```

Array1dI, Array1cI,

Array2ddI, Array2dcI, Array2cdI, Array2ccI,

...

Array1dF, Array1cF,

Array2ddF, Array2dcF, Array2cdF,

...

```

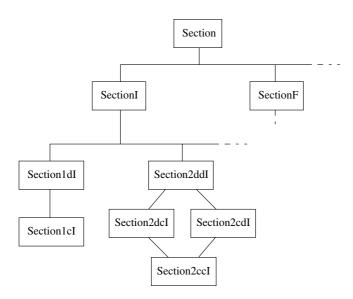

Generally speaking the class  $\mathtt{Array} ndc...T$  represents n-dimensional distributed array with elements of type T, currently one of  $\mathtt{I}, \mathtt{F}, \ldots$ , meaning  $\mathtt{int}, \mathtt{float}, \ldots^{\mathtt{1}}$ . The penultimate part of the class name is a string of n "c"s and "d"s specifying whether each dimension is collapsed or distributed. These correlate with presence or absence of an asterisk in slots of the HPJava type signature. The concrete  $\mathtt{Array}...$  classes implement a series of abstract interfaces. These follow a similar naming convention, but the root of their names is  $\mathtt{Section}$  rather than  $\mathtt{Array}$  (so  $\mathtt{Array2dcI}$ , for example, implements  $\mathtt{Section2dcI}$ ). The hierarchy of  $\mathtt{Section}$  interfaces is illustrated in figure 3. The need to introduce the  $\mathtt{Section}$

Fig. 3. The adJava Section hierarchy

<sup>&</sup>lt;sup>1</sup> In the inital implementation, the element type is restricted to the Java primitive types.

interfaces should be evident from the hierarchy diagram. The type hierarchy of HPJava involves a kind of multiple inheritance. The array type int [[\*, \*]], for example, is a specialization of *both* the types int [[\*, ]] and int [[, \*]]. Java allows "multiple inheritance" only from interfaces, not classes.

We will illustrate constructors of the Array classes in later examples. Here we mention some important members of the Section interfaces. The inquiry dat() returns an ordinary one dimensional Java array used to store the locally held elements of the distributed array. The member pos(i, ...), which takes n arguments, returns the local offset of the element specified by its list of arguments. Each argument is either a location (if the corresponding dimension is distributed) or an integer (if it is collapsed). The inquiry grp() returns the group over which elements of the array are distributed. The inquiry rng(d) returns the dth range of the array.

The second package in adJava is the communication library. The adJava communication package includes classes corresponding to the various collective communication schedules provided in the NPAC PCRC kernel. Most of them provide of a constructor to establish a schedule, and an execute method, which carries out the data movement specified by the schedule. The communication schedules provided in this package are based on the NPAC runtime library. Different communication models may eventually be added through further packages.

The collective communication schedules can be used directly by the programmer or invoked through invoked through certain wrapper functions. A class named Adlib is defined with static members that create and execute communication schedules and perform simple I/O functions. This class includes, for example, the following methods, each implemented by constructing the appropriate schedule and then executing it.

Use of these functions will be illustrated in later examples. Polymorphism is achieved by using arguments of class Section.

#### 3.2 Programming in the adJava interface

In this section we illustrate through an example (Fox's algorithm [11] for matrix multiplication) how to program in the adJava interface. We assume A and B are square matrices of order n, so C = AB is also a square matrix of order n. Fox's algorithm organizes A, B and C into sub-matrices on a P by P process array. It takes P steps. In each step, a sub-matrix of A is broadcast across each row of the processes, a local block matrix product is computed, and array B is shifted for computation in the next step.

We can program this algorithm in HPJava, using Adlib.remap to broadcast submatrices, Adlib.shift to shift array B, and Adlib.copy to copy data back

after shifting. The HPJava program is given in figure 4. The subroutine matmul for local matrix multiplication will be given in the next section.

This HPJava program is slightly atypical: it uses arrays distributed explicitly over process dimensions, rather than using higher-level ranges such as BlockRange to describe the distribution of the arrays. Hence, two-dimensional matrices are represented as four dimensional arrays with two distributed ranges (actually process dimensions) and two collapsed ranges (spanning the local block). This simplifies the initial discussion.

```

Procs2 p = new Procs2(P,P);

Range x = p.dim(0), y = p.dim(1);

on(p) {

float [[,,*,*]] a = new float [[x,y,B,B]];

float [[,,*,*]] b = new float [[x,y,B,B]];

... initialize a, b elements ...

float [[,,*,*]] c = new float [[x,y,B,B]];

float [[,,*,*]] tmp = new float [[x,y,B,B]];

for (int k = 0; k < P; k++) {

overall(i = x) {

float [[*,*]] sub = new float [[B,B]];

Adlib.remap(sub, a[[i, (x.idx(i) + k) % P, :, :]]);

// Broadcast sub-matrix of 'a'

overall(j = y)

matmul(c[[i, j, :, :]], sub, b[[i, j, :, :]]);

// Local matrix multiplication

}

Adlib.shift(tmp, b, 1, 0, CYCLIC);

// Cyclic shift 'b' in first dim, amount 1

Adlib.copy(b, tmp);

}

}

```

Fig. 4. Algorithm for matrix multiplication in HPJava

We can rewrite the program in pure Java language using our adJava interface. A translation is given in figure 5. This is an executable Java program. One can use (for example) mpirun to start Java virtual machines on  $P^2$  processors and let them simultaneously load the Fox class. This naive translation uses for loops plus at constructs to simulate the overall constructs. The function pairs on,no and at,ta adjust the field spmd.apg, which records the current active process group. The dynamic alteration of this group plays an non-trivial role in this program. The call to remap implements a broadcast because the temporary sub is replicated over the process group active at it's point of declaration. Within

the overall(i = x) construct, the locally effective APG is a row of the process grid. The rather complex code for section construction exposes various low-level inquiries (and one auxilliary class, Map) from the adJava runtime. The details are not particularly important here.

### 3.3 Improving the performance

The program for the Fox algorithm is completed by the definition of matmul. First in HPJava:

```

void matmul (float[[*,*]] c, float[[*,*]] b, float[[*,*]] c) {

for (int i=0; i<B; i++)

for (int j=0; j<B; j++)

for (int k=0; k<B; k++)

c[i,j]+=a[i,k]*b[k,j];

}</pre>

```

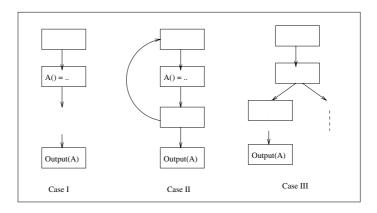

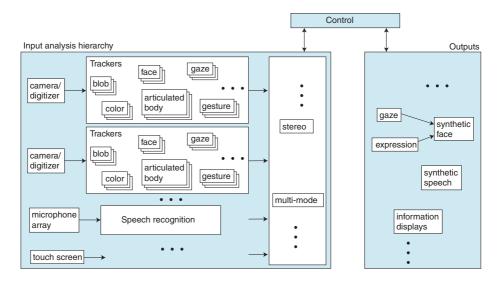

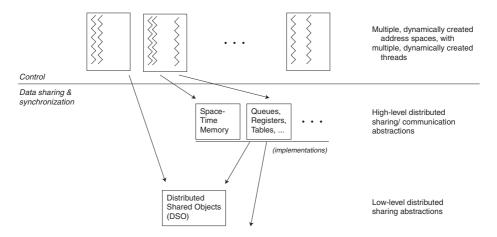

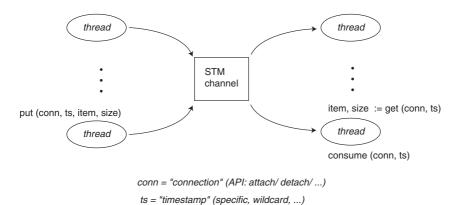

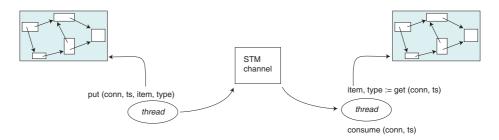

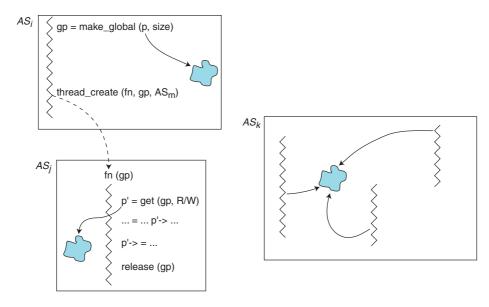

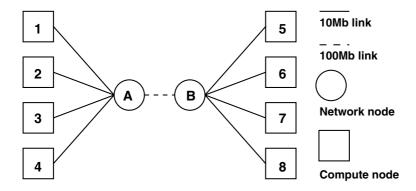

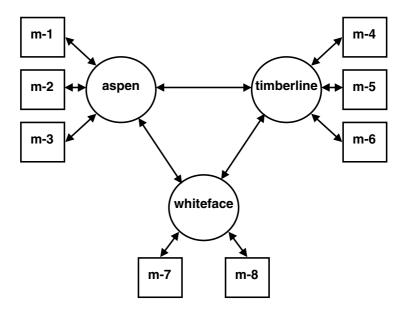

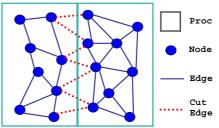

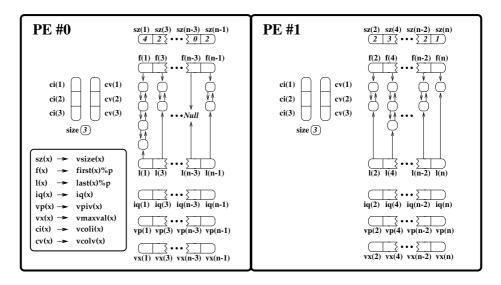

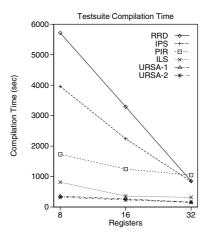

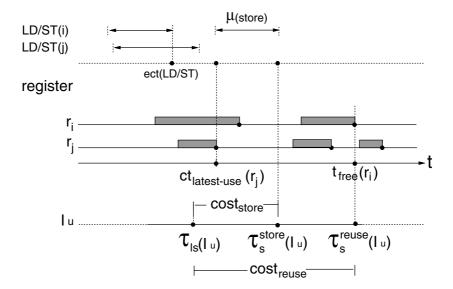

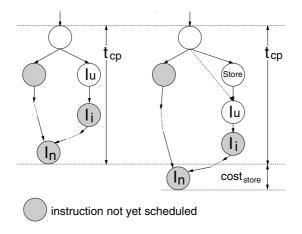

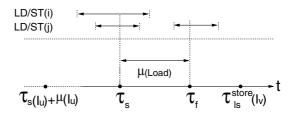

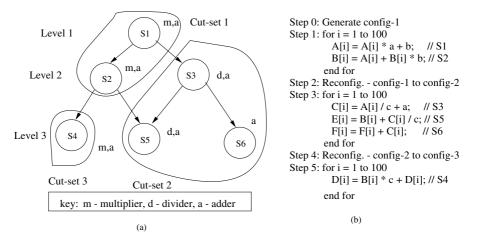

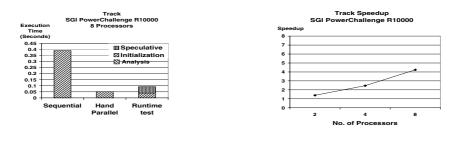

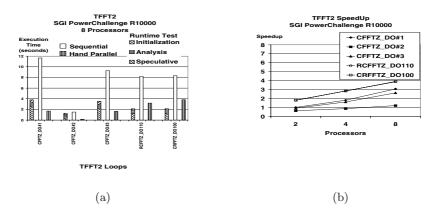

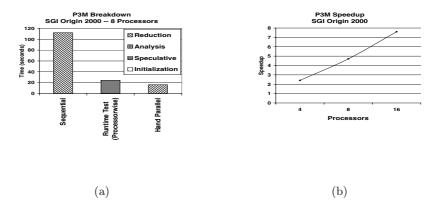

Translated naively to the adJava interface, this becomes: